近年著しく多数の製品に搭載され、販売されている『NAND Flash Memory』

仕組み、素子レベル、問題点をこのセクションでは簡易的に解説する

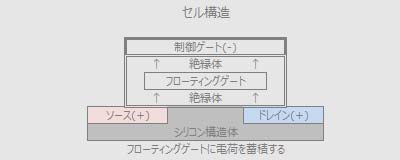

記録しているのは『電荷量』

フラッシュメモリはセルに電荷を蓄積し、その量(電圧)をデータとして表し、セルの集合体をページ/ブロックとして管理する

勿論半導体である為、定期的に電荷注入作業『リフレッシュ』を行わないと、電荷が抜けてしまうが

電荷抜けを防ぐ為に『絶縁体』の中に、電荷を保持出来る『フローティングゲート』と呼ばれる構造を構築している

ここで、絶縁されているのに何故電荷を蓄積できるのか?と疑問が出てくると思うが

絶縁部分に超高電圧を掛ける事で、電子を移動させている、つまり徐々に絶縁体が破壊されてしまう

この破壊は不可逆的で、徐々に電荷が漏れてしまう状態になり、最終的には絶縁が壊れ、電荷がすぐに抜けてしまう(寿命)

素子レベル

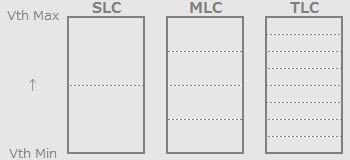

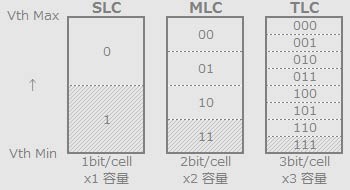

現在、NAND Flash Memoryのセル・レベルは大まかに3種類存在する

開発された当事は、1セルあたり1bit(0か1かの2段階)で記録する『SLC - Single-Level Cell』方式が主流だったが

大容量化を求める声が大きく、1セルあたり2bit(4段階)で記録する『MLC - Multi-Level Cell』へシフトし

依然としてMLCの需要も高いが、現在は1セルあたり3bit(8段階)で記録する『TLC - Triple-Level Cell』への移行が進もうとしている

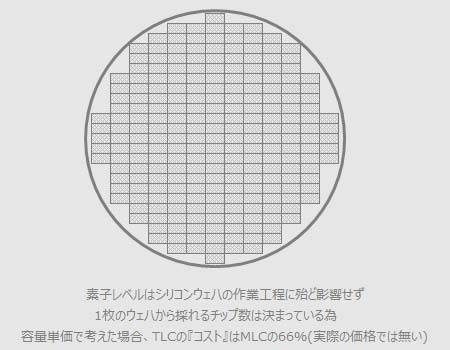

ここで注意することは、1セルの大きさは同じ世代の『製造プロセス』であれば殆ど同じ大きさであり

SLCは1倍、MLCは2倍、TLCは3倍のデータを記録できる為、純粋にコスト面で考えると、TLCが一番優れている

現在は競って製造プロセスの微細化が行われている、より小さく大容量となるが多値故の欠点がある、次項で説明しよう

多値化の二律背反

ここまでは、TLCが夢の技術の様に思ってしまうが、物理的な問題が大きく立ちはだかってしまう

フラッシュメモリが、電荷の蓄量(電圧)でデータを表す事を最初に説明したが、フローティングゲートに蓄えられる限界の電荷量は決まっている

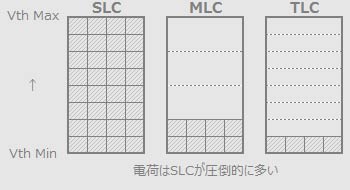

上記の図は、同じプロセスで製造されたSLC、MLC、TLCで、各素子レベルで電荷を蓄積した状態を単純に表した

SLCでは、最大32個/最小0個の電子で1bitを表すことが出来るが、MLC(2bit)では1/4の8個、TLC(3bit)では1/8の4個と

非常にデータを表せるマージンが狭い、これはあくまでも例えなので、実際には更にシビアな電荷の調整が必要となるし

絶縁体の破壊によって、漏れてしまう電荷も馬鹿にならなくなる、TLCが短寿命なのは、許容できるマージンが非常に少ない為となる

勿論データを保護する為に、強力なエラー訂正を備えているが、比較するとTLCではより高度なエラー訂正機構が必要となる

多値化の影響

TLCは高精度な電荷のコントロール、強力なエラー訂正のお陰で、現在は実用化されているが、方式故の問題点を挙げてみよう

勿論MLCでも下記の問題は存在するが、TLCとは比較にならないほど条件的には寛容である

1.書き込み速度が遅い

SLC、MLCと比較すると、注入する電荷の精度が求められる為、書き込み時の速度は非常に低速になってしまう

現在はクロックスピードを向上させ、相対的に書き込み速度も向上している

2.エラーが起きやすい

NAND Flash Memoryは有る程度のエラーを許容する事を前提で、強力なエラー訂正機構を備えているが、TLCの場合は顕著となる

3.負荷が高い

クロックスピードの向上はNAND、強力なエラー訂正はコントローラへの負荷となり、強いては消費電力(発熱)も増大してしまう

勿論、製造プロセスの微細化は、消費電力面での効果は有るが、より注入する電荷の精度が求められるようになる(問題1)

今回は、NANDフラッシュメモリの基本的な構造、素子レベル、TLCの問題点について、簡単な解説を行った

Back to Index